Скачать с ютуб Multi Cycle Datapath for MIPS Architecture - Class 32 в хорошем качестве

Скачать бесплатно и смотреть ютуб-видео без блокировок Multi Cycle Datapath for MIPS Architecture - Class 32 в качестве 4к (2к / 1080p)

У нас вы можете посмотреть бесплатно Multi Cycle Datapath for MIPS Architecture - Class 32 или скачать в максимальном доступном качестве, которое было загружено на ютуб. Для скачивания выберите вариант из формы ниже:

Загрузить музыку / рингтон Multi Cycle Datapath for MIPS Architecture - Class 32 в формате MP3:

Если кнопки скачивания не

загрузились

НАЖМИТЕ ЗДЕСЬ или обновите страницу

Если возникают проблемы со скачиванием, пожалуйста напишите в поддержку по адресу внизу

страницы.

Спасибо за использование сервиса savevideohd.ru

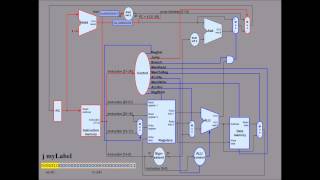

Multi Cycle Datapath for MIPS Architecture - Class 32

In our system, the execution of instructions is meticulously governed by a structured multi-cycle process designed to efficiently handle a spectrum of operations. Below, we outline the sequential steps that underscore our methodical approach: 1. Instruction Fetch: • All instructions commence with this fundamental step. The program counter (PC) determines the memory address to be accessed. • The instruction stored at the specified memory location is retrieved and stored in the Instruction Register (IR). • Simultaneously, the program counter is incremented by four, aligning it with the subsequent instruction. 2. Instruction Decode and Register Fetch: • Following fetch, the contents of the Instruction Register undergo decoding. • Depending on the instruction type, operands may be sourced from registers or require immediate computation. • For register instructions, designated register values are loaded into temporary registers A and B. Immediate instructions necessitate sign-extension and computation. • Manipulation of the program counter occurs in accordance with distinct instruction types. 3. Execution: • This phase dynamically adapts based on the instruction type. • Arithmetic and logical instructions prompt the ALU to operate on fetched operands as per the specified operation. • Memory reference instructions involve the computation of addresses for memory access. • Branch instructions entail operand comparisons to determine program flow alterations, while jump instructions require the calculation of target addresses. 4. Memory Access: • Memory access is pivotal, primarily for loading or storing data. • Load and store instructions necessitate memory access based on computed addresses, whereas other instructions may bypass this step entirely. 5. Completion: • The culmination of instruction execution involves storing results back into registers or memory. • For R-type instructions, results from the ALU are funneled back into registers. • Load instructions finalize by storing fetched data into designated registers, while store instructions transfer register data to memory. 6. Multi-Cycle Operation: • Each instruction type boasts a distinct cycle count, contingent upon its complexity and requisite operations. • Instructions are executed incrementally, with each cycle completing a specific operation within the instruction. Branch Execution Example: • Branch instructions merit special attention due to their potential to alter program flow. • Operand comparisons are conducted, and based on the outcome, the program counter is updated to facilitate branching or sequential continuation. Our meticulously structured multi-cycle approach ensures the efficient execution of instructions, adeptly accommodating diverse instruction types and operations within a systematic framework.