Скачать с ютуб Versal System Simulation with Riviera PRO Live Demo в хорошем качестве

Скачать бесплатно и смотреть ютуб-видео без блокировок Versal System Simulation with Riviera PRO Live Demo в качестве 4к (2к / 1080p)

У нас вы можете посмотреть бесплатно Versal System Simulation with Riviera PRO Live Demo или скачать в максимальном доступном качестве, которое было загружено на ютуб. Для скачивания выберите вариант из формы ниже:

Загрузить музыку / рингтон Versal System Simulation with Riviera PRO Live Demo в формате MP3:

Если кнопки скачивания не

загрузились

НАЖМИТЕ ЗДЕСЬ или обновите страницу

Если возникают проблемы со скачиванием, пожалуйста напишите в поддержку по адресу внизу

страницы.

Спасибо за использование сервиса savevideohd.ru

Versal System Simulation with Riviera PRO Live Demo

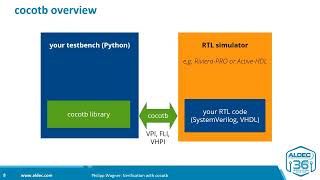

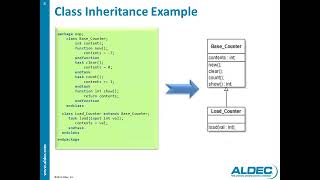

This video is a live demonstration of Versal System Simulation with Riviera-PRO. It’s an excerpt from the Aldec webinar titled “System Simulation of Versal ACAP Designs” Versal ACAP, developed by Xilinx/AMD, is a groundbreaking adaptable platform composed of AI Engine (AIE), Processing System (PS), Programmable Logic (PL), Network on Chip (NoC) and a wide range of hardened domain-specific IPs. Versal ACAP enables the efficient execution of complex algorithms and accelerates workloads, including machine learning, embedded computing, and high-performance computing. In this webinar, we will introduce Versal ACAP (and discuss the different types of simulation flows and models available) and QEMU (the open-source system emulator) and its co-simulation interface with Riviera-PRO. We will also show how to run a system simulation of a Versal example design. Riviera-PRO supports system simulation of Versal ACAP designs based on the Vitis™ hardware emulation flow for testing the interactions between PL, PS and AIE. The entire hardware emulation setup and system integration is done within the Vitis environment. It runs the AIE simulator for the graph application, Riviera-PRO’s simulator for the PL kernels, and QEMU for the PS host application. SystemC models are also available for the AIE and NoC, which can also be simulated in Riviera-PRO The full steps how to do this demo are available on Aldec Github page https://github.com/aldec/Riviera-PRO You will need to request a free evaluation of Riviera-PRO to run this demo. Submit your eval request here https://www.aldec.com/en/uvm-simulator