Скачать с ютуб Synchronous fifo design in verilog в хорошем качестве

Скачать бесплатно и смотреть ютуб-видео без блокировок Synchronous fifo design in verilog в качестве 4к (2к / 1080p)

У нас вы можете посмотреть бесплатно Synchronous fifo design in verilog или скачать в максимальном доступном качестве, которое было загружено на ютуб. Для скачивания выберите вариант из формы ниже:

Загрузить музыку / рингтон Synchronous fifo design in verilog в формате MP3:

Если кнопки скачивания не

загрузились

НАЖМИТЕ ЗДЕСЬ или обновите страницу

Если возникают проблемы со скачиванием, пожалуйста напишите в поддержку по адресу внизу

страницы.

Спасибо за использование сервиса savevideohd.ru

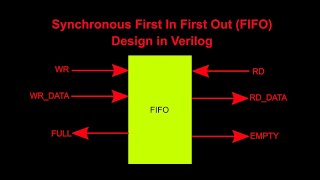

Synchronous fifo design in verilog

The synchronous FIFO design involves implementation of a memory array and associated write/read control logic at the RTL level using Verilog HDL. FIFO is an approach for handling program work requests from queues or stacks so that the oldest request is handled first. In hardware, it is either an array of flops or read/write memory that stores data from one clock domain and on request supplies the same data to other clock domains following FIFO logic.